CPU缓存层级分析与存储系统速率对比

存储层级设计背景

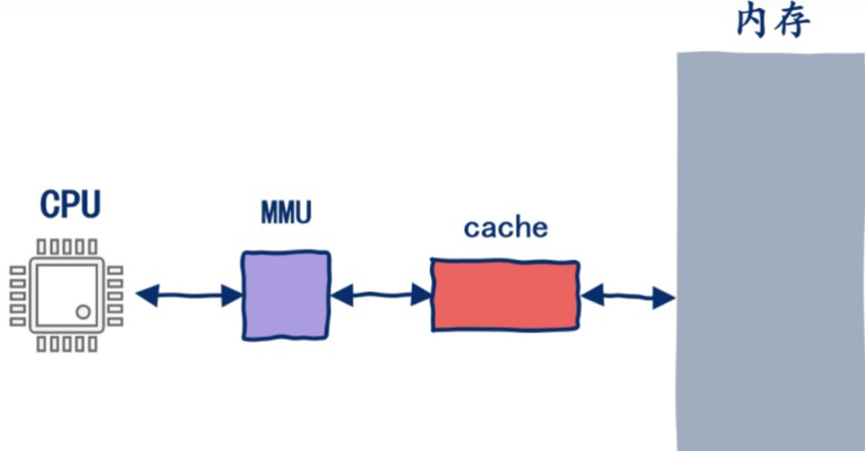

现代计算机系统中,CPU核心运算速率与主存访问速率之间存在数量级差距,该差距被称为"存储墙"。缓存层级设计通过在CPU与主存之间插入多级高速缓冲存储器,利用局部性原理减少平均内存访问延迟,弥合速度差距。

存储层级设计遵循以下基本原则:

- 越靠近CPU,存储速度越快,单位容量成本越高

- 容量随层级递增,延迟随层级递增,带宽随层级递减

- 利用时间局部性和空间局部性缓存热数据

CPU三级缓存架构分析

当前通用CPU普遍采用L1/L2/L3三级缓存设计,各层级设计目标和实现参数差异显著:

L1缓存

- 拓扑位置:CPU核心私有,每个核心独立实现

- 容量范围:32KB ~ 128KB / 核心(指令缓存+数据缓存分离设计,哈佛架构)

- 访问延迟:1 ~ 4 CPU时钟周期

- 带宽:~ 1TB/s ~ 2TB/s

- 设计目标:提供低延迟指令和数据访问,满足单核心流水线峰值需求

L2缓存

- 拓扑位置:CPU核心私有,每个核心独立实现

- 容量范围:256KB ~ 4MB / 核心

- 访问延迟:10 ~ 20 CPU时钟周期

- 带宽:~ 300GB/s ~ 500GB/s

- 设计目标:L1缓存的后备存储,容纳核心私有热数据,减少对L3和主存访问

L3缓存

- 拓扑位置:CPU封装内所有核心共享

- 容量范围:4MB ~ 128MB(服务器CPU可达数百MB)

- 访问延迟:30 ~ 80 CPU时钟周期

- 带宽:~ 100GB/s ~ 200GB/s

- 设计目标:容纳跨核心共享热数据,减少对主存访问,提供一致性缓存支持

缓存性能影响因素

- 缓存命中率:决定平均内存访问延迟,公式:平均延迟 = L1延迟 × L1命中率 + L2延迟 × (1-L1命中率) × L2命中率 + L3延迟 × (1-L1命中率)(1-L2命中率) × L3命中率 + 主存延迟 × (1-L1命中率)(1-L2命中率)(1-L3命中率)

- 关联度:越高关联度减少冲突不命中,但增加设计复杂度和访问延迟

- 缓存行大小:更大缓存行提高空间局部性,增加预取效率,但会导致带宽浪费和缓存污染

- 一致性协议:多核系统需要MESI/MESIF/MOESI等协议维护缓存一致性,带来额外通信开销

全存储层级速率参数对比

| 存储类型 | 典型访问延迟 | 典型峰值带宽 |

|---|---|---|

| CPU L1 缓存 | 1 ~ 4 ns | 1000 ~ 2000 GB/s |

| CPU L2 缓存 | 10 ~ 20 ns | 300 ~ 500 GB/s |

| CPU L3 缓存 | 30 ~ 80 ns | 100 ~ 200 GB/s |

| DDR4-3200 | 100 ~ 150 ns | ~ 50 GB/s |

| DDR5-6400 | 120 ~ 200 ns | ~ 100 GB/s |

| PCIe 4.0 NVMe SSD | 100 ~ 300 μs | 5 ~ 12 GB/s |

| PCIe 5.0 NVMe SSD | 80 ~ 200 μs | 10 ~ 16 GB/s |

| SATA 3.0 SSD | 500 ~ 1000 μs | ~ 0.5 GB/s |

| 7200RPM HDD | 5 ~ 10 ms | ~ 0.1 ~ 0.2 GB/s |

单位换算:1ms = 1000μs = 1,000,000ns。L1缓存访问速度比机械硬盘快6个数量级(百万倍),带宽差距达到四个数量级(千倍)。

关键结论

- 存储层级设计是解决CPU-内存性能差距的唯一工程可行方案,通过容量、延迟、成本的 trade-off 实现系统最优性价比

- L1/L2私有缓存保证单核心低延迟访问,L3共享缓存提供更大容量的多核共享缓冲,三级分工明确

- 缓存容量直接影响命中率,在同架构下,更大缓存可以稳定降低平均内存访问延迟,提升CPU有效IPC,对带宽敏感型工作负载(如游戏、多任务)提升显著

- 存储墙问题仍然存在,即使三级缓存设计,最坏情况下所有访问都未命中,CPU仍然会阻塞数百个周期等待主存响应

评论(0)

暂无评论